# Answers to Chapter 3 questions

#### Activity 3.1

| Input | values | Value               | Value | Output | Value   | Value | Output |

|-------|--------|---------------------|-------|--------|---------|-------|--------|

| Α     | В      | (a . <del>b</del> ) | (a.b) | +      | (a + b) | (a.b) |        |

| 0     | 0      | 0                   | 0     | 0      | 0       | 1     | 0      |

| 0     | 1      | 0                   | 1     | 1      | 1       | 1     | 1      |

| 1     | 0      | 1                   | 0     | 1      | 1       | 1     | 1      |

| 1     | 1      | 0                   | 0     | 0      | 1       | 0     | 0      |

Both truth tables have the same output (columns 5 and 8). Hence both expressions are the same.

#### Activity 3.2

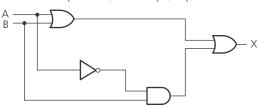

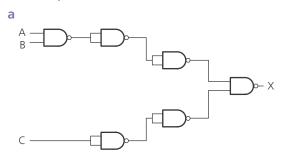

а

| Inp | Output |   |

|-----|--------|---|

| АВ  |        | Χ |

| 0   | 0      | 1 |

| 0   | 1      | 0 |

| 1   | 0      | 0 |

| 1   | 1      | 1 |

h

| Inp | Output |   |

|-----|--------|---|

| Α   | В      | X |

| 0   | 0      | 0 |

| 0   | 1      | 0 |

| 1   | 0      | 0 |

| 1   | 1      | 0 |

C

|   | Output |   |   |

|---|--------|---|---|

| Α | В      | С | Χ |

| 0 | 0      | 0 | 1 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 1 |

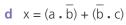

d

|   | Output |   |   |

|---|--------|---|---|

| Α | В      | С | Х |

| 0 | 0      | 0 | 1 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 1 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 0 |

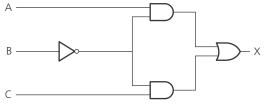

е

|   | Output |   |   |

|---|--------|---|---|

| Α | В      | С | Х |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 1 |

### Activity 3.3

**a** X = 1 if (A = 1 OR B = 1) OR (A = 0 AND B = 1)

| Inp | Output |   |

|-----|--------|---|

| Α   | В      | X |

| 0   | 0      | 0 |

| 0   | 1      | 1 |

| 1   | 0      | 1 |

| 1   | 1      | 1 |

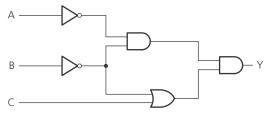

**b** Y = 1 if (A = 0 AND B = 0) AND (B = 0 OR C = 1)

|   | Output |   |   |

|---|--------|---|---|

| Α | В      | С | Y |

| 0 | 0      | 0 | 1 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 0 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 0 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 0 |

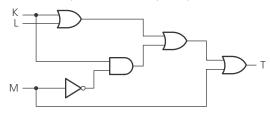

$\mathsf{C}$  T = 1 if (K = 1 OR L = 1) OR (K = 1 AND M = NOT 1) OR (M = 1)

|   | Output |   |   |

|---|--------|---|---|

| K | L      | М | T |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 1 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 1 |

|   | Output |   |   |

|---|--------|---|---|

| Α | В      | С | X |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 0 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 0 |

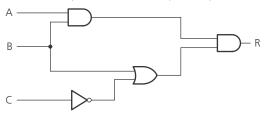

e R = 1 if (A = 1 AND B = 1) AND (B = 1 OR C = NOT 1)

|   | Output |   |   |

|---|--------|---|---|

| Α | В      | С | R |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 0 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 0 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 1 |

#### Activity 3.4

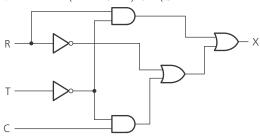

a X = 1 if (R = NOT 1) OR (C = 1 AND T = NOT 1) OR (R = 1 AND T = NOT 1)

|   | Output |   |   |

|---|--------|---|---|

| R | T      | С | Х |

| 0 | 0      | 0 | 1 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 1 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 0 |

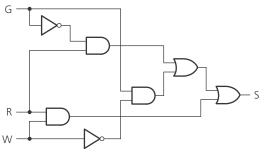

$\textbf{b} \quad S=1 \text{ if } (G=1 \text{ AND } W=\text{NOT 1}) \text{ OR } (G=\text{NOT 1} \text{ AND } R=1) \text{ OR } (W=1 \text{ AND } R=1)$

| Inputs |   |   | Output |

|--------|---|---|--------|

| G      | ĸ | W | S      |

| 0      | 0 | 0 | 0      |

| 0      | 0 | 1 | 0      |

| 0      | 1 | 0 | 1      |

| 0      | 1 | 1 | 1      |

| 1      | 0 | 0 | 1      |

| 1      | 0 | 1 | 0      |

| 1      | 1 | 0 | 1      |

| 1      | 1 | 1 | 1      |

## Activity 3.5

First logic circuit:

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Χ      |

| 0      | 0 | 0      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

which confirms this as an AND gate. Second logic circuit:

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Χ      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 1      |

which confirms this as an OR gate. Third logic circuit:

| Input | Output |  |

|-------|--------|--|

| Α     | Χ      |  |

| 0     | 1      |  |

| 1     | 0      |  |

which confirms this as a NOT gate.

#### Activity 3.6

| Inputs |   | Output from | Output from NAND |                   |

|--------|---|-------------|------------------|-------------------|

| Α      | В | С           | original circuit | gate only circuit |

| 0      | 0 | 0           | 1                | 1                 |

| 0      | 0 | 1           | 0                | 0                 |

| 0      | 1 | 0           | 1                | 1                 |

| 0      | 1 | 1           | 0                | 0                 |

| 1      | 0 | 0           | 1                | 1                 |

| 1      | 0 | 1           | 0                | 0                 |

| 1      | 1 | 0           | 1                | 1                 |

| 1      | 1 | 1           | 1                | 1                 |

which confirms that the two logic circuits have the same function.

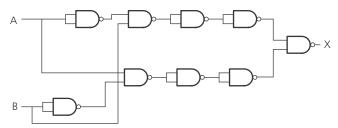

**b** NAND-gate only circuit:

**c** This gives the following truth table:

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Χ      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

which confirms that the logic circuit represents the XOR gate.

Activity 3.7

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Χ      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 0      |

which is the truth table for the NOR gate.

Activity 3.8

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Χ      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 0      |

which is the truth table for the NOR gate.

Activity 3.9

| Inputs |   |   | Output |

|--------|---|---|--------|

| Р      | Q | Ŕ | Х      |

| 0      | 0 | 0 | 0      |

| 0      | 0 | 1 | 1      |

| 0      | 1 | 0 | 0      |

| 0      | 1 | 1 | 1      |

| 1      | 0 | 0 | 0      |

| 1      | 0 | 1 | 1      |

| 1      | 1 | 0 | 0      |

| 1      | 1 | 1 | 1      |

which indicates that the logic circuit could be replaced by Input R only.